简化超高速数字系统中确定性延迟的设计

时间:2021-07-06 10:43来源:21 Dianyuan

摘要:实现确定性延迟是当今许多系统设计中讨论的主题。

实现确定性延迟是当今许多系统设计中讨论的主题。过去,人们一直在努力提高数据传输速度和带宽。如今的应用则越来越重视确定性——即要求数据包在精确的、可重复的时间点传送。

本文将在设备的层面讨论确定性这一主题,以及如何设计超高速数据转换和信号处理系统以保证确定性延迟。以下三个因素将决定确定性如何实现:

1. 采取措施减少数字设计组件中发生的亚稳态事件

2. 计算数字后端的延迟,确保多个数据链路通道之间(如HSSL)的数据对齐

3. 优化时间延迟的余量,保证不会因为 PVT 的变化而出现意外的不确定性。

具体来说,我们将考虑亚稳态的影响和同步系统的方案,并介绍如何在模拟和数字信号处理域之间的接口上保持确定性

管理超高速系统中数据转换器阵列的延迟的能力在复杂系统中非常重要,这些系统包括数字波束导向雷达、波束成形多载波通讯等。延迟会降低系统的性能。工程师的目标是将延迟控制在可知的范围内。如今有两种流行的 IC 数据接口:无许可证的 ESIstream和行业标准JESD204B(sub-classes 1 和2)。这两种接口都被广泛应用于连接数据转换器和逻辑器件(LD)如 FPGA和 ASIC。两者都承诺确定性,但在具体的实现上有所不同。本文将阐述,考虑到优秀的灵活性、较低的开销和绝对延迟,ESIstream将是最佳的选择。

延迟的定义

延迟的简单定义是操作和响应之间的时间差。在采样数据系统中,通常我们最关心的是最大延迟。对于以硬件为点的本文,不确定性的来源以及如何管理这些来源是一个关键问题。确定性是一个简单的需求,即系统对于给定的一组输入产生相同的结果。不论环境或启动条件如何变化,结果都是可预测的,并排除随机因素。本质上,确定性系统提供了有限的响应。

免责声明:本文若是转载新闻稿,转载此文目的是在于传递更多的信息,版权归原作者所有。文章所用文字、图片、视频等素材如涉及作品版权问题,请联系本网编辑予以删除。

我要投稿

近期活动

- 安森美汽车&能源基础设施白皮书下载活动时间:2024年04月01日 - 2024年10月31日[立即参与]

- 2023年安森美(onsemi)在线答题活动时间:2023年09月01日 - 2023年09月30日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年08月01日 - 2023年08月31日[查看回顾]

- 【在线答题活动】PI 智能家居热门产品,带您领略科技智慧家庭时间:2023年06月15日 - 2023年07月15日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年06月01日 - 2023年06月30日[查看回顾]

分类排行榜

- 汽车电子电源行业可靠性要求,你了解多少?

- 内置可编程模拟功能的新型 Renesas Synergy™ 低功耗 S1JA 微控制器

- Vishay 推出高集成度且符合 IrDA® 标准的红外收发器模块

- ROHM 发布全新车载升降压电源芯片组

- 艾迈斯半导体推出行业超薄的接近/颜色传感器模块,助力实现无边框智能手机设计

- 艾迈斯半导体与 Qualcomm Technologies 集中工程优势开发适用于手机 3D 应用的主动式立体视觉解决方案

- 维谛技术(Vertiv)同时亮相南北两大高端峰会,精彩亮点不容错过

- 缤特力推出全新商务系列耳机 助力解决开放式办公的噪音难题

- CISSOID 和泰科天润(GPT)达成战略合作协议,携手推动碳化硅功率器件的广泛应用

- 瑞萨电子推出 R-Car E3 SoC,为汽车大显示屏仪表盘带来高端3D 图形处理性能

编辑推荐

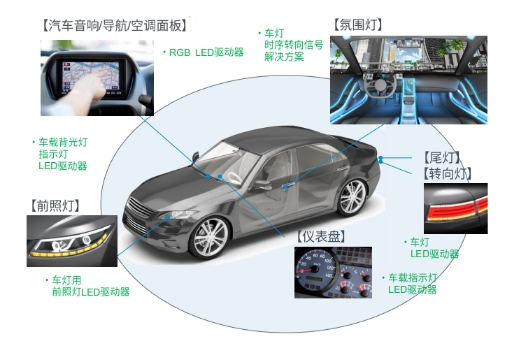

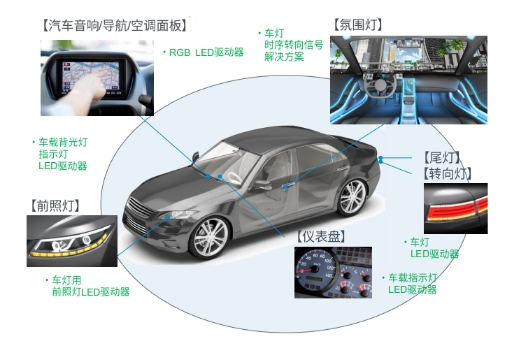

小型化和稳定性如何兼得?ROHM 推出超小型高输出线性 LED 驱动器 IC,为插座型 LED 驱动 IC 装上一颗强有力的 “心脏”

众所周知,LED的驱动IC担负着在输入电压不稳定的情况下,为LED提供恒定的电流,并控制恒定(可调)亮度的作用。无论是室内照明,还是车载应用,都肩负着极为重要的使命。

- 关于反激电源效率的一个疑问

时间:2022-07-12 浏览量:10200

- 面对热拔插阐述的瞬间大电流怎么解决

时间:2022-07-11 浏览量:8954

- PFC电路对N线进行电压采样的目的是什么

时间:2022-07-08 浏览量:9597

- RCD中的C对反激稳定性有何影响

时间:2022-07-07 浏览量:7207

- 36W单反激 传导7~10M 热机5分钟后超标 不知道哪里出了问题

时间:2022-07-07 浏览量:5981

- PFC电感计算

时间:2022-07-06 浏览量:4192

- 多相同步BUCK

时间:2010-10-03 浏览量:37872

- 大家来讨论 系列之二:开机浪涌电流究竟多大?

时间:2016-01-12 浏览量:43167

- 目前世界超NB的65W适配器

时间:2016-09-28 浏览量:60030

- 精讲双管正激电源

时间:2016-11-25 浏览量:128142

- 利用ANSYS Maxwell深入探究软磁体之----电感变压器

时间:2016-09-20 浏览量:107564

- 【文原创】认真的写了一篇基于SG3525的推挽,附有详细..

时间:2015-08-27 浏览量:100305