利用频域时钟抖动分析加快设计验证过程

摘要:Usingfrequencydomainclockjitteranalysistospeedupdesigncertificationprocess...

| Using frequency domain clock jitter analysis to speed up design certification process |

| 作者:安捷伦科技 Akihiko Oginuma 时间:2009-03-04 来源:电子产品世界 浏览评论 |

引言

随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展。目前的重点是针对比特误码率,在时钟性能和系统性能之间建立直接联系。我们将探讨参考时钟的作用和时钟抖动对数据抖动的影响,并讨论在E5052B信号源分析仪(SSA)上运行的Agilent E5001A精确时钟抖动分析应用软件所配备的全新测量技术。该应用软件提供了前所未有的强大能力,可以对随机抖动(RJ)和周期抖动(PJ)分量超低RJ测量和实时抖动频谱分析,使您能够提高设计质量。我们还将对新解决方案的实时测量功能进行讨论,这一功能能够加快设计验证过程。

参考时钟在高速串行应用中的作用

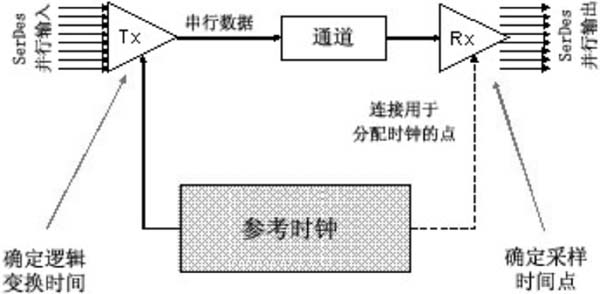

图1是参考时钟的主要分量。发射机通常将一组速率较低的并行信号转换成串行数据流。信号经过一条包括多个背板和电缆的传输通道进行传送。接收机通常会解释输入的串行数据,从中分离出时钟,再把串行数据重新转换成并行数据流。在许多诸如此类的说明中,参考时钟更多地被视为一种分量但不是主要分量,而在高速串行数据系统中,我们必须承认参考时钟是一种主要分量。通常,参考时钟的振荡速率远远低于数据速率,但它会在发射机中成倍增长。发射机使用参考时钟来确定串行数据流中的逻辑变换定时。发射的数据中包括参考时钟的特征。在接收机中可能会出现两种不同的情况。如果未分配参考时钟,则接收机会利用锁相环(PLL)从数据流中还原时钟――并利用该时钟定位采样时间点。如果已分配参考时钟,则接收机会同时使用数据信号和参考时钟来定位采样点。

图1 参考时钟的作用

参考时钟是最终的系统定时源。它为发射机、已分配和未分配的时钟系统提供时基,而接收机的时钟恢复电路可以重现参考时钟特征。现在我们将探讨时钟抖动如何在系统发射机中进行传输。

发射机必须用适当的因数乘以参考时钟获得数据速率,才能确定逻辑变换定时。例如,对于100 MHz参考时钟和5 Gb/s输出信号,发射机将用PLL给参考时钟乘以因数50。PLL乘法器不仅放大时钟抖动,还引入其自身的抖动,主要是PLL压控振荡器(VCO)的RJ。频率乘以因数n的结果是相位噪声功率载波比乘以n2,所以抖动迅速变大。

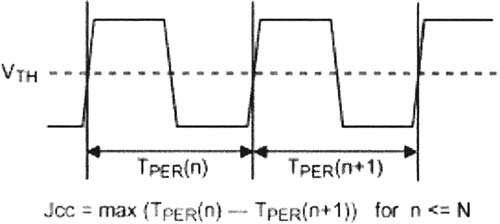

发射机中的PLL乘法器具有一定的频率响应,通常是如图3所示的二阶响应。非均匀频率响应会产生一个值得注意的问题:时钟抖动实际上有什么影响?如果PLL非常出色且带宽为零,那么它将过滤掉所有的时钟抖动,而为发射机提供无抖动时基。当然,零带宽意味着无限锁定时间,所以我们不得不综合考虑,但是PLL带宽越窄,参考时钟加入数据中的抖动就越小。确定时钟是否能在系统中正常工作且符合预期的BER要求,需要对抖动频谱进行详细测试。

图3 PLL频率响应

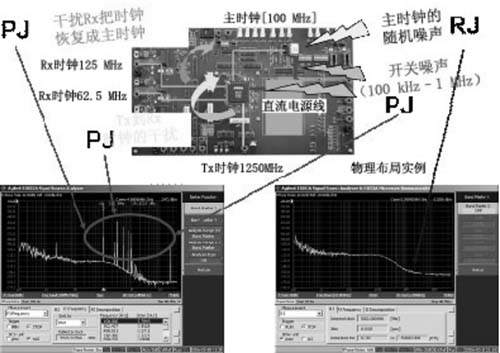

真实的抖动源

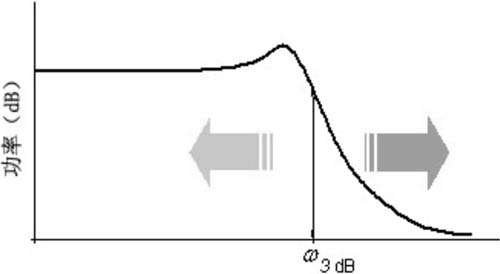

如果观察实际环境中的高速数字电路,您会发现许多抖动源,如图4所示。跟我们前面讨论的一样,时钟信号通常分配给多个IC,时钟频率可能进行乘法和/或除法运算。假设来自晶体振荡器的参考时钟具有较低的抖动,因为IC带来的附加噪声或其他设备产生的干扰,所以经过乘法或除法运算的输出时钟也可能不是非常干净。

一个主要污染源就是开关电源的噪声。开关频率一般为100 kHz到1 MHz。开关电源噪声可能会注入时钟信号线路,它在左下图中显示为PJ。

其他周期抖动分量的来源可能是数据或时钟线路的干扰,经互调后可能位于时钟线上,也显示为PJ分量。只要PJ分量表现的远离时钟频率,它就极有可能插入带通滤波器(或低通滤波器)来消除这些抖动。然而,问题是周期抖动在什么时间接近时钟频率,因为高频高Q滤波器很难得到。参考时钟的RJ也一样,时钟除法器可能添加宽带噪声,这可能会使输出时钟信号的RJ增加。

要诊断各种问题,设计人员必须表征有关电路物理布局和/或工作环境下的时钟抖动。

图4 实际环境中的抖动源

全面分析时钟信号要求达到飞秒级精度,只有相位噪声测量技术才能达到这种精度。相位噪声分析提供两种主要测量:S?(f?)和?(t),它们根据相位噪声测量带宽限制收集时钟的所有相位信息。

在相位噪声分析仪上分析RJ可以完成两个重要目标。首先,通过集成RJ频谱,可以提取预定带宽中的相应RJ高斯分布宽度。其次,通过分析S?(f?)的幂级数行为确定RJ的主要原因(图5)。

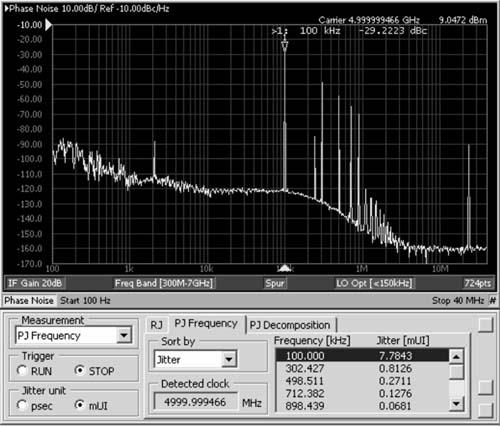

在相位噪声频谱中可以看到PJ分量的杂散。所以PJ频率知识对于诊断问题非常有帮助。参考每个PJ频率的PJ rms也能帮您了解每个PJ分量对总体时钟抖动的影响,查看去除主要PJ分量之后总体抖动的变化(图6)。

图5 分析相位噪声测量的RJ

图6 相位噪声测量的PJ频率通过先进的体系结构进行实时抖动测量

与传统的抖动测量模式不同,带有E5001A软件的E5052B SSA可以对相位噪声测量进行实时抖动分析。该仪器使用PLL提供参考源。它能够自动检测时钟频率,在几毫秒内把内置参考源自动调谐为时钟频率,测量相位检波器保持PLL所产生的噪声信号。它在250 MSa/s ADC上捕获噪声信号,从而可以进行100 MHz抖动带宽测量。该测量涵盖OC-192抖动分析范围。实时FFT可以获得频域数据,并能显著提高测量速度。例如,1 kHz到100 MHz带宽的测量每次只需0.3秒。

图7 Agilent E5052B信号源分析仪的先进体系结构

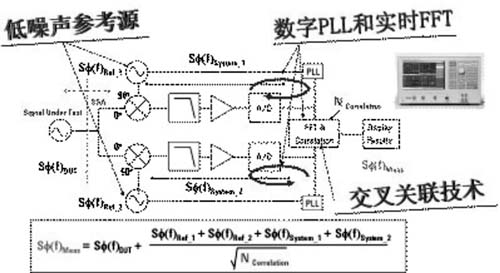

利用交叉关联技术获得出色的抖动本底噪声

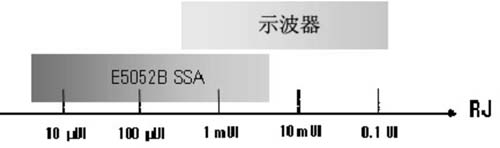

E5052B抖动测量分辨率和本底噪声非常低,通常10Gbps速率时的RJ本底噪声仅为几飞秒。由于ADC的动态范围有限,且其内部参考时基的剩余抖动较大,高性能(实时或采样)示波器的抖动本底噪声通常在一百飞秒以上。E5052B通过检测基带(其中较大的载波信号已删除)的相位噪声来保持宽动态范围。E5052B利用两个独立的内部测量通道之间的独特交叉关联技术,将抖动测量极限扩大到低于其内部时基的残余抖动。(参见图7)与目前的高性能示波器相比,E5052B利用这种交叉关联技术把抖动本底噪声降低了100倍到1,000倍(图8)。

图8 利用交叉关联技术获得的出色抖动本底噪声

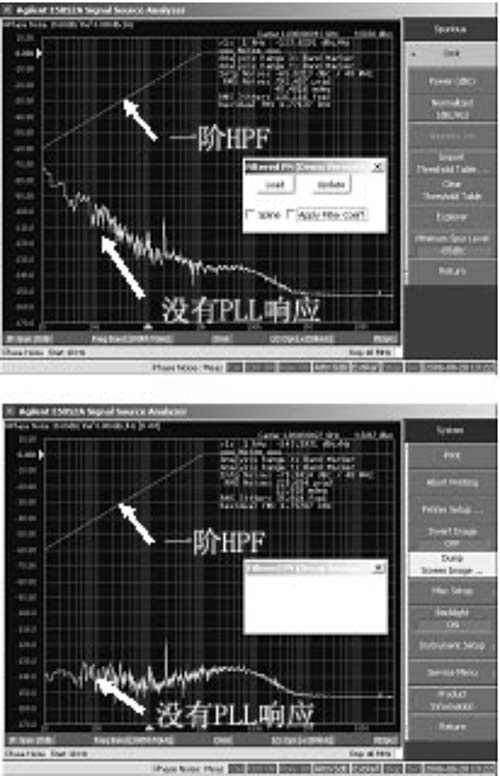

实时仿真PLL响应

图9表示直接应用于时钟相位噪声信号的PLL响应功能的结果。您可以看到如何消除频谱的不同部分,使您可以分析与应用相关的抖动。E5052B对相位噪声测量的实时抖动分析功能可加快您的设计进程。E5052B SSA可以导入任何PLL响应函数,使您可以轻松快速地仿真设备到设备的PLL响应。

图9 仿真PLL响应

结语

对于高速串行数据应用,时钟抖动分析的主要目的是确定参考时钟的抖动对系统比特误码率的影响。最精确的方法是对时钟应用发射机(和接收机)在最坏情况下的传递函数,并测量获得的时钟RJ和PJ。在E5052B上运行的E5001A精确时钟抖动分析软件改变了传统的抖动测量方式,它不仅能以飞秒级分辨率对时钟抖动进行全面分析,而且具有出色的易用性和实时抖动分析功能,可以帮助您加快设计验证过程。

http://www.21dianyuan.com/supply/supplyhome/company.php?company_id=1544

- 安森美汽车&能源基础设施白皮书下载活动时间:2024年04月01日 - 2024年10月31日[立即参与]

- 2023年安森美(onsemi)在线答题活动时间:2023年09月01日 - 2023年09月30日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年08月01日 - 2023年08月31日[查看回顾]

- 【在线答题活动】PI 智能家居热门产品,带您领略科技智慧家庭时间:2023年06月15日 - 2023年07月15日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年06月01日 - 2023年06月30日[查看回顾]

- 汽车电子电源行业可靠性要求,你了解多少?

- 内置可编程模拟功能的新型 Renesas Synergy™ 低功耗 S1JA 微控制器

- Vishay 推出高集成度且符合 IrDA® 标准的红外收发器模块

- ROHM 发布全新车载升降压电源芯片组

- 艾迈斯半导体推出行业超薄的接近/颜色传感器模块,助力实现无边框智能手机设计

- 艾迈斯半导体与 Qualcomm Technologies 集中工程优势开发适用于手机 3D 应用的主动式立体视觉解决方案

- 维谛技术(Vertiv)同时亮相南北两大高端峰会,精彩亮点不容错过

- 缤特力推出全新商务系列耳机 助力解决开放式办公的噪音难题

- CISSOID 和泰科天润(GPT)达成战略合作协议,携手推动碳化硅功率器件的广泛应用

- 瑞萨电子推出 R-Car E3 SoC,为汽车大显示屏仪表盘带来高端3D 图形处理性能

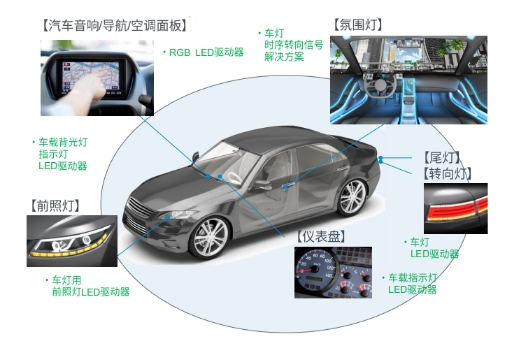

众所周知,LED的驱动IC担负着在输入电压不稳定的情况下,为LED提供恒定的电流,并控制恒定(可调)亮度的作用。无论是室内照明,还是车载应用,都肩负着极为重要的使命。

- 关于反激电源效率的一个疑问

时间:2022-07-12 浏览量:10214

- 面对热拔插阐述的瞬间大电流怎么解决

时间:2022-07-11 浏览量:8970

- PFC电路对N线进行电压采样的目的是什么

时间:2022-07-08 浏览量:9612

- RCD中的C对反激稳定性有何影响

时间:2022-07-07 浏览量:7220

- 36W单反激 传导7~10M 热机5分钟后超标 不知道哪里出了问题

时间:2022-07-07 浏览量:5992

- PFC电感计算

时间:2022-07-06 浏览量:4201

- 多相同步BUCK

时间:2010-10-03 浏览量:37875

- 大家来讨论 系列之二:开机浪涌电流究竟多大?

时间:2016-01-12 浏览量:43173

- 目前世界超NB的65W适配器

时间:2016-09-28 浏览量:60034

- 精讲双管正激电源

时间:2016-11-25 浏览量:128162

- 利用ANSYS Maxwell深入探究软磁体之----电感变压器

时间:2016-09-20 浏览量:107571

- 【文原创】认真的写了一篇基于SG3525的推挽,附有详细..

时间:2015-08-27 浏览量:100327