临界模式 Buck 电感计算公式

时间:2016-11-17 15:48来源:世纪电源网

摘要:编者按:在龙腾活动参赛帖《反激变压器设计要领》中,网友与楼主的问答引发了有关Buck电感计算的讨论,因与原帖主题有所偏离,楼主专门就Buck电感计算发帖,分享经验。

编者按:在龙腾活动参赛帖《反激变压器设计要领》中,网友与楼主的问答引发了有关Buck电感计算的讨论,因与原帖主题有所偏离,楼主专门就Buck 电感计算发帖,分享经验。

mingchristian:版主是否考虑开一贴讲解BUCK电路设计,虽然之前做的都成功,但就是没一个系统的全方位理解。或者版主能不能共享一下你们完成的BUCK和BOOSTPFC的资料方法

nc965:

承蒙夸奖,谢谢。

Buck以及PFC-Boost这类拓扑,只是个电感,没有漏感问题,远远不用像反激变压器这样纠结,想系统的全方位讲解和理解,感觉都无从着力,论坛中也没见有太多的提问,不用讲吧?

mingchristian:

先感谢版主,一直关注你各个帖子,都很精彩。关于这个反激的设计,以往都是用先定D 、f、效率、△B然后去算扎比,IPK , LP NP等,然后验算验证,再就是实测VDS和IPK大小看设计是否合理。感觉设计的电路效率也还可以,EMC勉勉强强。布满匝数只能通过更改线径做。

BUCK做过几款,单纯的电感,算法是看着简单,也许是我没理解深刻。一个22W非隔离,做匝数和感量不一样,效率会相差甚远,更甚,做了低感量的,EMC会比高感量的差很多。当时没深刻阅读EMC要领一,昨天刚把画好的板发出去打样,很快就能去尝试。

还有一个50W的非隔离,第一次做非隔离那时候,做的电流值在烤机1小时后电流有明显的跌落(是跌落还是上升,忘记了),且多次CS电阻炸了。也没分析什么情况。所以我觉得,BUCK电路是不是也有很多我没看见没理解的。还是只是我在BUCK上的经验太少,显浅的我都没懂。

nc965:

既然话都说到嘴边了,不防再罗嗦几句。这位同学做事情显然很认真,啥都想搞个明白,“然”还不满足,还要所以“然”,赞一个。

对于Buck、Boost电感,在以下关键问题上与反激变压器是一样的,因此设计考虑也是一样的:

1、磁饱和强度 Bs 是优化指标,估计一个 Bs 值就可能偏离最佳值,偏离最佳值多少就是偏离最优化多少。

2、优化的方法是一样的,即:调整匝数或者频率(非定频驱动的话),上下求索,找到最佳绕组结构。不是感觉“效率还可以”就行了,也许还有效率更高的另外一个绕组结构。同样,绕组参数也可以是离散的,仍然可以按整层来控制,以方便工艺和辅助绕组的需求。

3、匝数、电感量对变换器整体影响规律是一样的,即:较小的 匝数对应较小的电感量和较高的频率,这表现为较小的铜损和可能较大的磁损,还可表现为提高输入电压低端的效率而可能降低其高端的效率,并以这些因素权衡最终优化点。

4、磁损与铜损的关系是一样的,即:在最大损耗的那个工作点,二者没有热交换即是最佳,温升最低。

这里面体现的是同样的设计思想:

1、绕组结构决定变压器(电感)性能。

2、计算得出来的还不行,还要能绕得出来。

3、能绕出来还不行,还要优化,还可能有更好的、也绕得出来的绕组结构。

4、找到更好的还不行,还要证明这是最好的,其他都不如这个好。

在某种意义上说,反激变压器与Buck、Boost电感本质上是一样的,他们都是受最大磁偏电流 Ipk 控制、受最大磁饱和强度 Bs 控制,都是储能--释能这样的工况。

反激变压器与Buck、Boost电感的根本区别有二:

1、反激拓扑原边付边的电压应力显著提高,这直接导致开关损耗和二极管反向恢复损耗加剧以及磁应力的增加,变换效率的显著降低。

2、反激变压器有漏感问题,漏感意味着能量转换效率降低,无论是原边或者付边的漏感能量处理都是损耗,漏感还导致电压尖峰,使上一个问题加剧。

其中,电压应力是硬伤,是拓扑决定的。但是,漏感却是人为可以掌控的,因此,控制漏感就成了反激变压器设计和优化优先考虑的目标,也是反激变压器与Buck、Boost电感设计的最大不同。

因此,漏感即是反激变压器设计最重要的参数,漏感这个参数与气隙有莫大的关系,气隙越小漏感越低,漏感是被气隙放大的,这些观念同样也贯穿反激变压器设计的始终。

你关心的BUCK电感的设计优化例子,今天才发现我在另外的跟贴里有较详细的说明,你可以参考一下:非隔离低PF的LED电路的计算(Buck)(←文章将于下篇分享给大家)

Mingchristian:

按照你表格的方法算,输入180VAC~240VAC,输出80V 0.24A ,期望F=60KHZ △B=0.3 骨架为EPC17 AE=22.8算IPK=IO*2=0.48A

当NP=274时(之前用的是NP=138电感),LM=3905UH(实际取值4050uh)

验算:voll=180*1.414=255V

FS=(250-80)*80/(4050*0.48*0.48*250)=58KHZ

TON=1000/58*80/250=5.5US

实际测试效率最高89%。

因为此次是用MT7834 IC 所以开始的计算是用MT提供的表格。

把MT那串很长的公式抽出来如下:

TONMAX=VO/VDCMIN/FS

LP=(1.414*(VACMIN-0.58*VO)^2*TONMAX*效率/(3.14*VACMIN*IO)

IPK=(VDCMIN-VO)/LP/TONMAX

NP=IPK*LP/AE/B

与以上提到同样的条件,算出参数是:TONMAX=5.24US , LP=877UH IPK=1.042A NP=134TS

同样的板换这个变压器,效率上91%

但MT的公式看不是很懂,,,李版你的方法我能在哪里改善一下让效率上91%

nc965:

BUCK,效率到95以上才正常。

Mingchristian:

那李工能不能帮我算个变压器让我试试,我的板子按照你的EMC方法布板,只有一个pi型滤波224+3.3mh+224,桥前只有一个07D431K 内置MOS,D用ES2J EMC测试效果比较好,尝试去掉工字电感,效率并无提升多少。所以我认为问题还是在这个变压器上,输出80V0.24A,用EPC17是否合理,是否需要用大的骨架,这个变压器和匝数计算,多次计算都出不来好的效果

希望李工给予帮助

nc965:

那个BUCK电感计算表格没有时间整理出来,但基本原理是明确的,公式也是有的,还可能涉及PFC等方面的问题。

其他问题说一下:

你的EMC设计思路和效果既然不错,希望你在原帖跟一下贴共享一下你的体会,那贴发出几年了,不明白为什么一个反馈都没有,奇怪!

简单的PI形滤波结构不一定就是最好的结构,要结合X电容和桥后电容通盘考虑,或许可以省下一些电容。

压敏用431是不靠谱的,现在小电源都喜欢用471,我也是不赞同的。这涉及现在的市电波动范围,已经超出多数人的估计。应该用到511、561才对。

Mingchristian:

关于EMC那个其实帖子已经写好放在电脑里面,但就是因为BUCK这个效率一直做不好,最高92%,觉得是一个问题,所以一直想是把这个解决了那发出来就不是一个有明显问题的产品。

如果表格里的公式就是李工你给我的设计思路,我下午换一个EFD20的骨架试试,0.33线200TS 还是3900uh,

感谢李工的指导

nc965:

IPK=IO*2=0.48A,你不是高PF的?

Mingchristian:

是高PF的IC。

高PF的IC是其他的计算吗?按1.3(1.15)倍算IPK?

nc965:

高 PF 的 Buck 不能这样算,难怪你总是不对。

对于你这个案例,Ipk=4*0.24*1.208=1.16A

把上面公式整理一下就是:

Ipk=PFC*2*0.24*K=4*0.24*1.208=1.16A

其中:

PFC设定,高PF时为2,否则为1,这个明白吧?155楼有推导。

系数K是一个大于1的数:

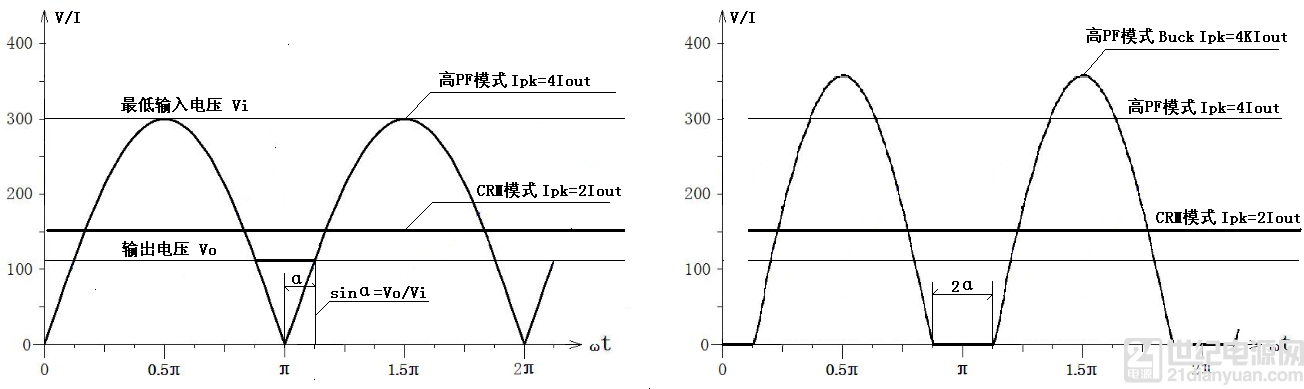

高PF模式的Buck,PFC控制是不完整的,当输入馒头波电压低于输出电压时,Buck没有输出,如图所示:

即:高PF模式的Buck,需要在 π-2α 时段内输出其他模式在全周期π时段内相同的能量,其最高 Ipk 必然增加一个系数K才行。

ltpzm:

能否指明下高底PFC的数值范围都是多少?

楼主:

这里,高低PF是以控制方式来区分,高PF和低PF(PFC和非PFC控制)是完全不同的控制算法,因此 Ipk 显著不同。

高低PF也可以从效果上来区分,比如填谷电路,PF可以到0.9,勉强也算高PF,但不能用这个公式,因为它不是因为PFC控制产生的高PF。

ltpzm:

你的意思是PF值低于0.9都算低PF?可以这样理解吗?

楼主:

不可以。

在这里,低PF可以理解成没有APFC控制的,也包括某些人出于某种目的用APFC控制的芯片做成的低PF电源,都不能用考虑Ipk的PFC系数。

mingchristian:

上周一个非隔离180VAC~240VAC输入,高PF的BUCK电路,用论坛里DCDC的方法算,IPK取1.2*IO这样的方法,算出来的结果明显不对,后来搜索到李版多年以前的贴,CRM模式算,IPK=2*IO 算出来结果测试,RCS炸了,今天根据李版这里的方法,算出来的电路效率92%+ , 比FAE提供的表格算出来的效率要高一点点。

但是,根据李版说,非隔离电路做到95%以上才正常,感觉很困难,电路哪里还能再优化?

输入180VAC时频率60KHZ,非常准,220VAC输入时频率73khz , 测试RCS两端电压测IPK(是否正确?),最高点0.17V,有一尖峰0.52V ,RCS=0.81 那IPK=0.64A?????,算出△B=0.17

而且180VAC输入的VRCS更小,我测试点是不是不对???

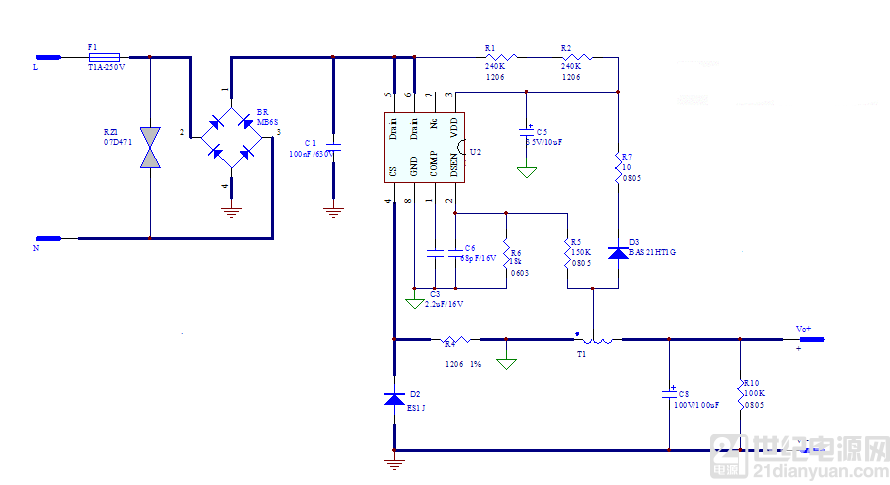

原理图如下,RCS=R4=0.81R

输入180VAC~240VAC 输出80V0.24A 变压器EFD20 AE=31 94砸 785uh 这个参数还能怎么优化?FS=60KHZ

楼主:

降低频率,用多股线等,此外,你的Ipk,dB,貌似都没有抓到特征波形。

mingchristian:

没上传图片是因为一直在纠结,取上图中R4俩端电压VIPK,除以R4,算出来IPK这个方法是不是正确的。现在电感用0.33*1漆包线,下午再测试一个45KHZ多股线的试试。

EFD20 0.14*7漆包线 NP=130T LP=1080UH

频率约在45khz 220VAC频率为53khz 实测VIPK=1.04V RCS=0.81R 计算IPK=1.284A 计算△B=0.344

按所说,取了较低的频率,多股线,效率没有明显的提升,从92.1%提升至92.4% ,取消工字电感,效率为93.5%,

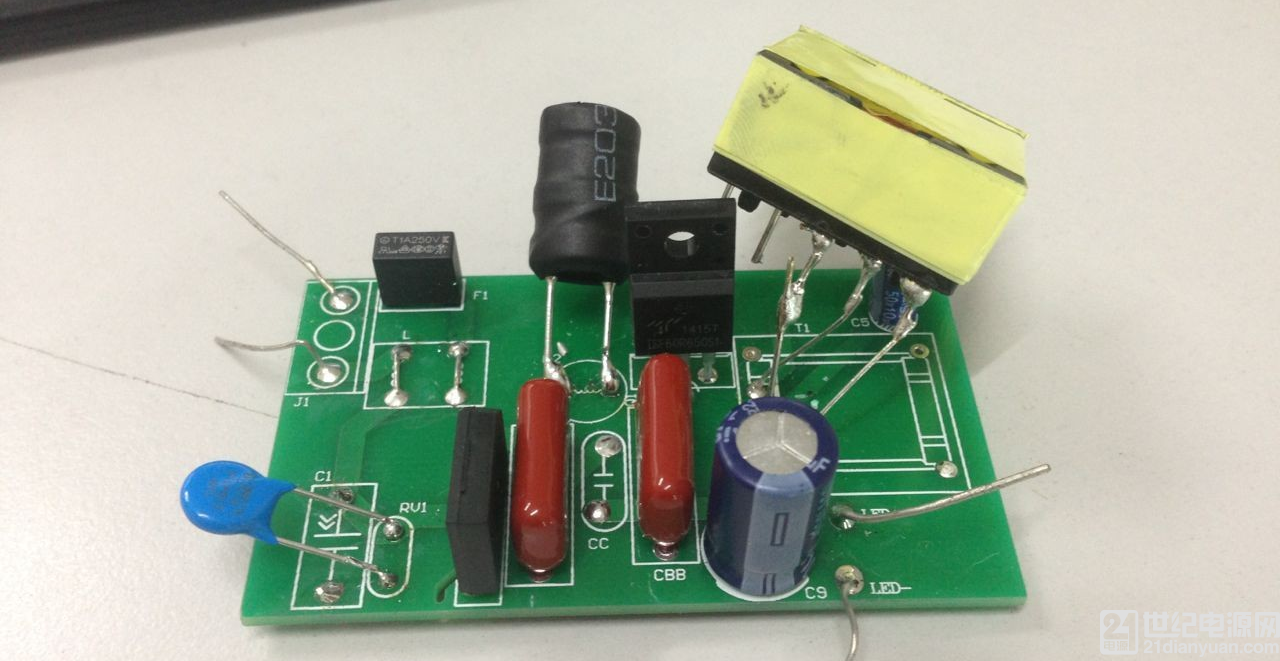

内置MOS , D用ES2J 桥堆用贴片MB10S , 板上的插件还有俩个CBB224,一个压敏,一个10uf50V 一个100uf100v 一个保险,

非隔离能达到95%以上才算正常,李工这句话做起来非常难啊,非隔离达到95%,难度相当于反激达到90%的水平,还是反激达到93%以上的水平啊?

楼主:

那是指低PF-Buck,高PF电流应力增很多,你能到93%不错了,但仍然有优化余地。反激做到93%很正常哈,同样原因,高PF反激上93%就很难了,高PF全电压反激上93%几乎就是不可能的了。

mingchristian:

继续跟帖,跟之前同样参数,输入180~240VAC 输出80V0.625A 50W FS=45KHZ 用外置MOS D取ES3J MOS用TSF60R650S1

EFD20 NP=130TS LP=410UH 板上器件有07D431 KBP210 FUSE CBB224*2 电解100V100UF

效率为93.7%。130砸要磨410uh,磨了半个小时,手都酸了,感觉磁芯应该小了。测试完EMC后改用EFD25,NP=70TS ,LP=410UH 板上器件恢复一样,效率为94.08%,这次终于把效率提到94%了。关于EMC测试,之前30W或以内(最大用30W80V测试)的小板,内置MOS ,用EMC(一)那帖子的方法,桥前一个压敏,桥后CBB224*2+工字3.3MH 变压器无 屏蔽,二极管无并联RC,有足够余量通过,这次用50W ,桥前用压敏+CX224 桥后用CBB224*2+工字5.6MH 变压器屏蔽 , MOS RGATE=300R D RC=330PF+68R//68R

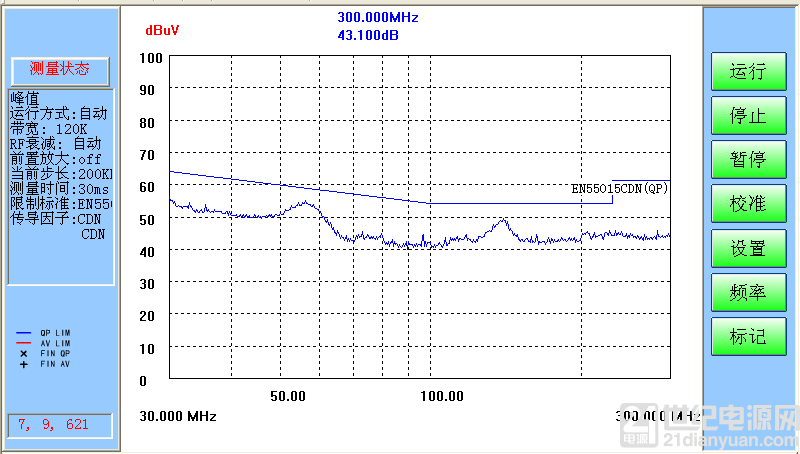

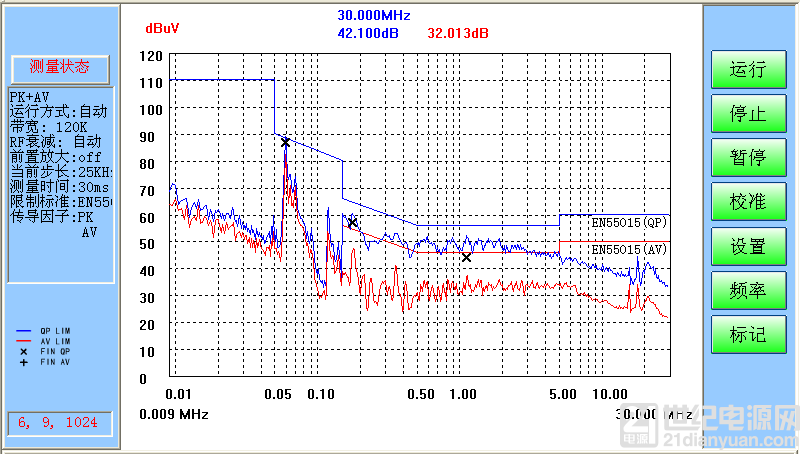

辐射测试有足够余量通过,传导测试在100KHZ之前有一个很高的尖峰,1MHZ之前段余量只有3dB ,前段那个很高的尖峰只能通过增加CX来对付?还有其他好的办法不?而1MHZ前的地方,在不增加共模的情况下,是要增加差模电感的感量吗?已经5.6mh了。

CZ电容最大加到222,效果好像不明显

楼主:

首先,电感还应优化,我大致算了一下,你最低输入180Vac,输出50W80V,Ipk=2.8A,按Bs=0.3的EFD25磁芯计算,有以下绕组可选:

其中应该有一个是最高效率的。当然,你有其他线径,还可以进一步精选,找到那个最佳的。

还有以下措施可提高效率

1、输出电压,比如提高到120V(PFC\THD特性可能变差),可显著提高效率。

2、差模电感对效率有显著影响,差模滤波是一个π形滤波结构,要减少差模电感,就必须增加电容,还要考虑前后两个电容的搭配,才能使差模电感最小。最佳搭配是:X电容--差模电感--桥前CBB--桥--桥后CBB。

根据你50W的功率,可以计算出差模电感在220Vac时的电流应力(约0.34A),按照工字磁芯的安匝数,1012磁芯可以做到3.3mH,0810磁芯可以做到1.8mH,超过此值意味着饱和,因此你传导有尖刺。

3、共模电感也影响效率,也要尽量小(个头、感量),你如果按照我之前的方法做板,EMC应力应该不大,可先不要共模调试,最后必要时才加进共模,从最小感量(比如100uH)开始加,直到满意。

mingchristian:

看了版主的建议,顺势产生了一些问题:

1、VI与VO相差越大,效率会高,这句以前好像是在网上哪里看过的,而此版主的说法相反,那就是占空比越小效率越高,这个怎么推到理解?

2、差模电感一直不会怎么测试饱和,这里借此机会问一下。然后,在论坛搜索到版主你的工字电感计算表格,220Vac时的电流应力,是PI/VI*1.5倍这么推算吗?对照表格的最大饱和电流,那安匝数这个怎么得出来。对工字电感了解非常浅,希望帮助耐心解答

3、共模电感计算在论坛帖子也不多,之前一直是实测的方法,逐渐加大,但尺寸和线径这个都无详细计算,我觉得应该也是有跟工字电感一样的公式吧。

楼主:

1、Buck,降压幅度越小效率越高,不降压效率最高,这不应该有疑问吧?

2、那个表格中的参数是实测的,很大致。

3、共模对效率的影响是铜损,减少感量即减少铜损

mingchristian:

工字电感还没到,所以还不能测试之前EMC尖峰的问题

改输出110VDC 功率尽量接近,所以这次计算是VO=110V IO=0.455A 50W , 还有一个VO=110V IO=0.22A

在之前的尝试中,50W最高效率是94.08% 20W最高效率是93.5%

这次效率上图,板上依然没有共模差模电感

50W: 0.444*110/51.3=95.204%

20W: 0.215*110/24.9=94.98%

虽然效率提升心里早有预先,可是一下提升了1个多点,逼近95% 还是非常惊喜的,那低PF岂不是能更高?

楼主:

低PF可以到96、7%,也有做到98%的,看条件。

mingchristian:

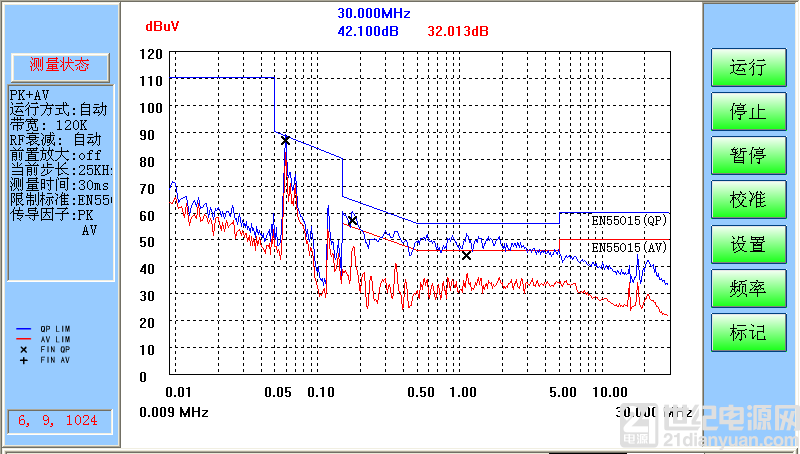

打样的工字电感到了,拿着测了一下,规格参数有所改变,之前是输出80V0.625A , 为了测试效率, 然后把板子改成了VO=110V IO=0.455A 带灯测试带100V,先看一个之前输出80V0.625A,输入一个CX154 工字电感3.3mh(怀疑饱和) , 一个07D431K 传到入下图

这次测试没把板改成原来的规格,沿用VO=110V IO=0.22A规格,原因就一个,懒!

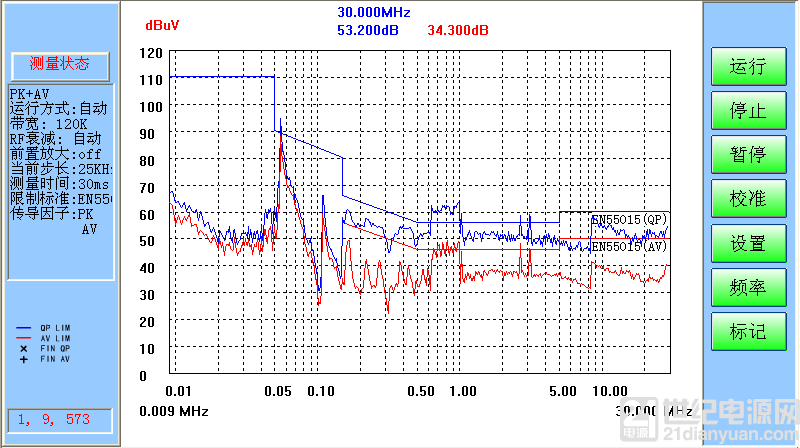

输入端用原来的一个3.3mh工字电感,一个07D431K CX154取消。结果如下图

更改规格后,在没有CX的情况 传到不过。。。。。尖峰依然存在

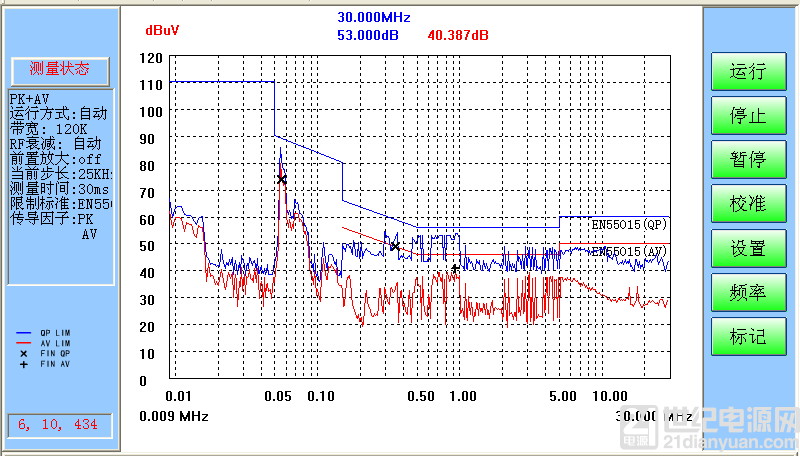

把3.3MH工字电感改为更大磁芯,2mh电感 尖峰减少,依然存在,传到通过,与之前相比,增大工字电感 后,减少一个CX 成本减少

附上被我玩得不要不要的PCB ,此板只是为了测试用,并不是出货板,吐槽请轻手。

传到余量一般,估计把板子整干净,效果应该会更好。

更多精彩讨论,请点击原文链接:http://bbs.21dianyuan.com/thread-237877-1-1.html

更多技术文章请关注官方微信,搜索微信号V-21dianyuan或扫描以下二维码

免责声明:本文若是转载新闻稿,转载此文目的是在于传递更多的信息,版权归原作者所有。文章所用文字、图片、视频等素材如涉及作品版权问题,请联系本网编辑予以删除。

我要投稿

近期活动

- 安森美汽车&能源基础设施白皮书下载活动时间:2024年04月01日 - 2024年10月31日[立即参与]

- 2023年安森美(onsemi)在线答题活动时间:2023年09月01日 - 2023年09月30日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年08月01日 - 2023年08月31日[查看回顾]

- 【在线答题活动】PI 智能家居热门产品,带您领略科技智慧家庭时间:2023年06月15日 - 2023年07月15日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年06月01日 - 2023年06月30日[查看回顾]

分类排行榜

- 汽车电子电源行业可靠性要求,你了解多少?

- 内置可编程模拟功能的新型 Renesas Synergy™ 低功耗 S1JA 微控制器

- Vishay 推出高集成度且符合 IrDA® 标准的红外收发器模块

- ROHM 发布全新车载升降压电源芯片组

- 艾迈斯半导体推出行业超薄的接近/颜色传感器模块,助力实现无边框智能手机设计

- 艾迈斯半导体与 Qualcomm Technologies 集中工程优势开发适用于手机 3D 应用的主动式立体视觉解决方案

- 维谛技术(Vertiv)同时亮相南北两大高端峰会,精彩亮点不容错过

- 缤特力推出全新商务系列耳机 助力解决开放式办公的噪音难题

- CISSOID 和泰科天润(GPT)达成战略合作协议,携手推动碳化硅功率器件的广泛应用

- 瑞萨电子推出 R-Car E3 SoC,为汽车大显示屏仪表盘带来高端3D 图形处理性能

编辑推荐

小型化和稳定性如何兼得?ROHM 推出超小型高输出线性 LED 驱动器 IC,为插座型 LED 驱动 IC 装上一颗强有力的 “心脏”

众所周知,LED的驱动IC担负着在输入电压不稳定的情况下,为LED提供恒定的电流,并控制恒定(可调)亮度的作用。无论是室内照明,还是车载应用,都肩负着极为重要的使命。

- 关于反激电源效率的一个疑问

时间:2022-07-12 浏览量:10189

- 面对热拔插阐述的瞬间大电流怎么解决

时间:2022-07-11 浏览量:8944

- PFC电路对N线进行电压采样的目的是什么

时间:2022-07-08 浏览量:9587

- RCD中的C对反激稳定性有何影响

时间:2022-07-07 浏览量:7199

- 36W单反激 传导7~10M 热机5分钟后超标 不知道哪里出了问题

时间:2022-07-07 浏览量:5974

- PFC电感计算

时间:2022-07-06 浏览量:4184

- 多相同步BUCK

时间:2010-10-03 浏览量:37868

- 大家来讨论 系列之二:开机浪涌电流究竟多大?

时间:2016-01-12 浏览量:43163

- 目前世界超NB的65W适配器

时间:2016-09-28 浏览量:60027

- 精讲双管正激电源

时间:2016-11-25 浏览量:128120

- 利用ANSYS Maxwell深入探究软磁体之----电感变压器

时间:2016-09-20 浏览量:107561

- 【文原创】认真的写了一篇基于SG3525的推挽,附有详细..

时间:2015-08-27 浏览量:100299