传导超标整改:分析、建模、验证

时间:2019-01-04 11:37来源:21Dianyuan

摘要:本文将结合一个传导超标的案例,进行分析、建模,最后对策验证。主要目的是演示这个过程,举一反三,在整改的过程中达到事半功倍的效果。

* 本文作者:拒绝变帅,感谢作者的辛勤付出。

关于传导和辐射整改,实际中看到比较多的是出现超标后,直接尝试不同的方法后找出对策,运气好的第一招就有效,几分钟搞定,运气不好的最后一招才搞定可能一周、一个月就过去了。

对于传导和辐射整改的整改方法,我自己把它划为两大类:

① 逐一尝试:预先列出几十条整改方法,一条条试

② 对症下药:结合理论分析和经验,有针对性地下对策

本文将结合一个传导超标的案例,进行分析、建模,最后对策验证。 主要目的是演示这个过程,举一反三,在整改的过程中达到事半功倍的效果。

文章大纲

1. 基础知识回顾

1.1 散热片、屏蔽层、Y 电容的作用机理

1.2 差模噪音路径和模型

1.3 共模噪音路径和模型

2. 实际案例:分析和建模

2.1 骚扰路径分析

2.2 建模和模型参数确认

3. 根据分析,提出建议对策

4. 进行试验验证

5. 结论

基础知识回顾

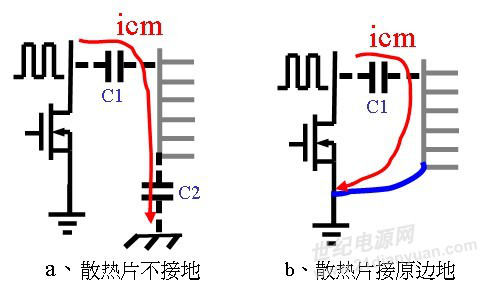

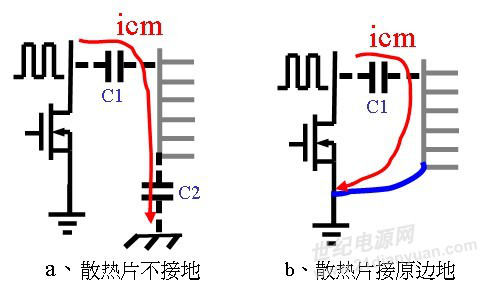

电脑没有画图软件,只能用 PowerPoint 来画。以反激拓扑为例,下面先看看散热片的作用,见下图:

其中:

C1 为 MOS 与散热片的寄生电容

C2 为散热片与大地 PE 之间的寄生电容

✔ 散热片悬空时,共模电流 icm 会通过 C2 流到大地,从而被 LISN 拾到,导致共模干扰增加。

✔ 散热片接地时,共模电流 icm 被短路到原边干扰源的地,不经过 LISN,即降低了共模干扰。

1. 大家都知道会增加漏感,但很少人会去进一步想到底增加了多少漏感?比如从原来的 10uH 变到了12uH,还是 20uH?其实微小变动想增加到 20uH 都很难。

再说说对效率的影响。

这里的效率指的是平均效率 (25%、50%、75%、100%这4个载的效率和取平均)。漏感影响最大的是100%,随着负载的降低,漏感的影响越来越小直至可忽略,最后对平均效率的影响很多都是在0.1%以下,基本可忽略。

2. 调整绕组对 EMI 的影响有多少 dB,我在另一个贴中《小功率开关电源中辅助供电 VCC 设计相关总结》中有解释。其实说多少 dB 可能都是基于自己所碰到的情况,主观色彩较浓。

3. 以上是基于小功率开关电源来说的,对于大功率的,情况可能不一样,而且成本和空间比较宽裕,不需要抠那么细。

看看变压器屏蔽层的作用,见下图:

有无 Y 电容的区别:

从上面的分析可以看出,其实散热片、屏蔽、Y 电容,对 EMI 的作用机理是一样的,即都为干扰信号提供一条低阻抗回路,让干扰信号返回源端,让其不从 LISN 经过。

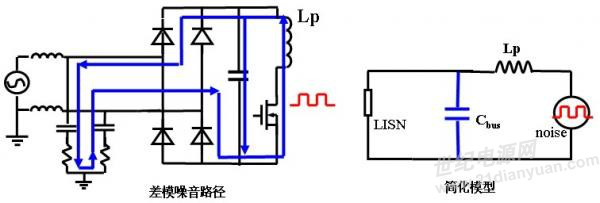

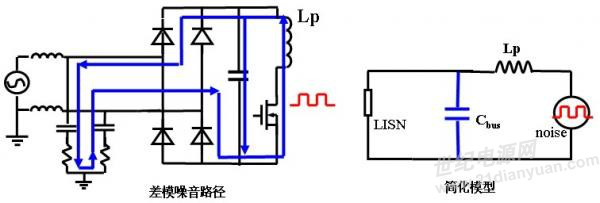

下面看一下共模和差模路径以及对应的简化模型。以反激拓扑为例,同时由于副边的 dV/dt 一般较小,这里省去了,突出主要部分。

下面是差模的路径和模型:

从以上可以看出 Cbus 对 EMI 的影响,尤其是冷热机的差异。 电解的 ESR 随着温度的升高而降低,有利于干扰信号的流过,这也是一些案例热机后 EMI 会变好的原因之一。

下面是共模路径和简化模型:

从以上的模型可以看出,不管是差模还是共模,EMI 的本质就是欧姆定律。无非就是串联分压和并联分流,通过各种方法让 LISN 少分压、少分流而已。

EUT 产生的干扰噪声依次通过 LISN 内部的高通滤波器和 50Ω 电阻,在 50Ω 电阻上得到相应的信号值送到接收机进行分析。

实际案例

这是个 90W 的例子,PFC+flyback 的两极结构。基本情况如下:

① 桥前的 EMI 滤波器架构是:小 X 电容+小共模+大 X 电容+大共模;

② 桥后就是 PFC+flyback 电路,重点不讲电路,这里就不画图了;

③ 原副边的地之间接有 Y 电容,Y 电容的一个脚套有磁珠;

④ 输出端的 Vo 与 GND 之间有个小共模。

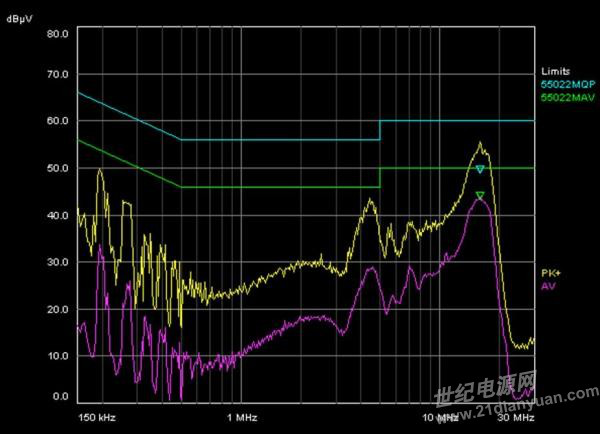

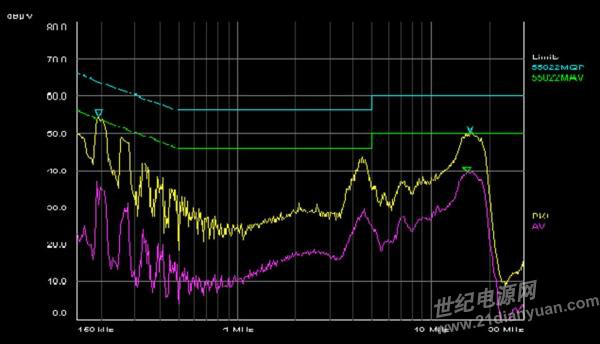

现象 (测试时输出 GND 与大地连接) 是:

现象分析

▪ 传导在10几 MHz 的高频处超标,一般是共模干扰超标引起的。

▪ 测试是输出与地连接的情况下超了,说明地线参与了耦合干扰,从这也证明了这是共模干扰超标。

此共模干扰从源端产生,经变压器的一二次侧寄生电容传到次级,一部分被 Y 电容传回原边,另一部分经过输出端的共模阻隔后通过负载的接地线传到 LISN。

根据以上分析以及共模路径图,建立如下模型:

其中:

Z2 为变压器一二次侧寄生电容的阻抗;

Z3 为 Y 电容和所串的磁珠的阻抗;

Z4 为输出共模的阻抗;

Z5 为 LISN 的阻抗。

从以上模型图可以得知:

① 要降低共模干扰 Vlisn,有多种方法,比如降低 Vnoise、增大 Z2、减小 Z3、增大 Z4。

② 降低 Vnoise 就是从源端解决了,一般会影响效率,改动太大。

③ 增大 Z2,就是减小变压器一二次侧寄生电容,这个目前已是比较优化的结构,改动效果不明显。

④ 减小 Z3,可以通过增大 Y 电容实现。

⑤ 增加 Z4,就是提升输出共模的阻抗。

方法建议

经过实测,增大 Y 电容可以降 5dB,但会导致漏电流超出客户规格,无法导入。

那就看增加 Z4 阻抗了,其实热机后会变差也是由于 Z4 的阻抗特性发生了变化,尝试过降低 Z4 的温度,但由于电流较大,温度仍然较高,效果不明显。

难道没办法了吗?

细看模型,Z3 回路还包括磁珠的阻抗,是否可以通过去掉磁珠来解决呢?

下面去掉后的实测效果:

结果是改善3~4dB,虽然没有加大 Y 电容的效果好,但有足够的裕量了,同时不影响效率,还降低了成本,两全其美啊!

其实,还要去确认辐射。结果辐射在 30M~40M 的地方变差了 2dB。好在即使变差也有足够的裕量,不用再去头疼了。至此,问题解决!

此帖通过分析、建模和最后验证,说明了传导整改是有章可循的,有了理论指导,实践起来就会事半功倍。 案例本身不难,希望是通过例子能够举一反三,在整改中发挥作用。 技术这东西,说穿了就那么回事,在没说穿的时候又有多少人可以自己看穿。

* 查看更多内容,下载仿真文件,请点击进入 21Dianyuan 社区

* 本文为21Dianyuan 社区原创文章,未经授权禁止转载。请尊重知识产权,违者本司保留追究责任的权利。

关于传导和辐射整改,实际中看到比较多的是出现超标后,直接尝试不同的方法后找出对策,运气好的第一招就有效,几分钟搞定,运气不好的最后一招才搞定可能一周、一个月就过去了。

对于传导和辐射整改的整改方法,我自己把它划为两大类:

① 逐一尝试:预先列出几十条整改方法,一条条试

② 对症下药:结合理论分析和经验,有针对性地下对策

本文将结合一个传导超标的案例,进行分析、建模,最后对策验证。 主要目的是演示这个过程,举一反三,在整改的过程中达到事半功倍的效果。

文章大纲

1. 基础知识回顾

1.1 散热片、屏蔽层、Y 电容的作用机理

1.2 差模噪音路径和模型

1.3 共模噪音路径和模型

2. 实际案例:分析和建模

2.1 骚扰路径分析

2.2 建模和模型参数确认

3. 根据分析,提出建议对策

4. 进行试验验证

5. 结论

基础知识回顾

电脑没有画图软件,只能用 PowerPoint 来画。以反激拓扑为例,下面先看看散热片的作用,见下图:

其中:

C1 为 MOS 与散热片的寄生电容

C2 为散热片与大地 PE 之间的寄生电容

✔ 散热片悬空时,共模电流 icm 会通过 C2 流到大地,从而被 LISN 拾到,导致共模干扰增加。

✔ 散热片接地时,共模电流 icm 被短路到原边干扰源的地,不经过 LISN,即降低了共模干扰。

1. 大家都知道会增加漏感,但很少人会去进一步想到底增加了多少漏感?比如从原来的 10uH 变到了12uH,还是 20uH?其实微小变动想增加到 20uH 都很难。

再说说对效率的影响。

这里的效率指的是平均效率 (25%、50%、75%、100%这4个载的效率和取平均)。漏感影响最大的是100%,随着负载的降低,漏感的影响越来越小直至可忽略,最后对平均效率的影响很多都是在0.1%以下,基本可忽略。

2. 调整绕组对 EMI 的影响有多少 dB,我在另一个贴中《小功率开关电源中辅助供电 VCC 设计相关总结》中有解释。其实说多少 dB 可能都是基于自己所碰到的情况,主观色彩较浓。

3. 以上是基于小功率开关电源来说的,对于大功率的,情况可能不一样,而且成本和空间比较宽裕,不需要抠那么细。

看看变压器屏蔽层的作用,见下图:

有无 Y 电容的区别:

从上面的分析可以看出,其实散热片、屏蔽、Y 电容,对 EMI 的作用机理是一样的,即都为干扰信号提供一条低阻抗回路,让干扰信号返回源端,让其不从 LISN 经过。

下面看一下共模和差模路径以及对应的简化模型。以反激拓扑为例,同时由于副边的 dV/dt 一般较小,这里省去了,突出主要部分。

下面是差模的路径和模型:

从以上可以看出 Cbus 对 EMI 的影响,尤其是冷热机的差异。 电解的 ESR 随着温度的升高而降低,有利于干扰信号的流过,这也是一些案例热机后 EMI 会变好的原因之一。

下面是共模路径和简化模型:

从以上的模型可以看出,不管是差模还是共模,EMI 的本质就是欧姆定律。无非就是串联分压和并联分流,通过各种方法让 LISN 少分压、少分流而已。

EUT 产生的干扰噪声依次通过 LISN 内部的高通滤波器和 50Ω 电阻,在 50Ω 电阻上得到相应的信号值送到接收机进行分析。

实际案例

这是个 90W 的例子,PFC+flyback 的两极结构。基本情况如下:

① 桥前的 EMI 滤波器架构是:小 X 电容+小共模+大 X 电容+大共模;

② 桥后就是 PFC+flyback 电路,重点不讲电路,这里就不画图了;

③ 原副边的地之间接有 Y 电容,Y 电容的一个脚套有磁珠;

④ 输出端的 Vo 与 GND 之间有个小共模。

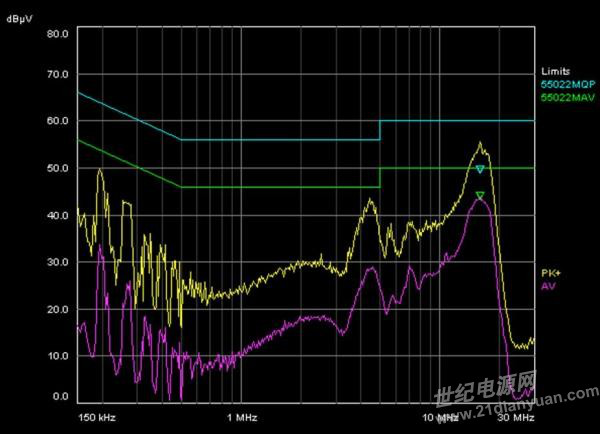

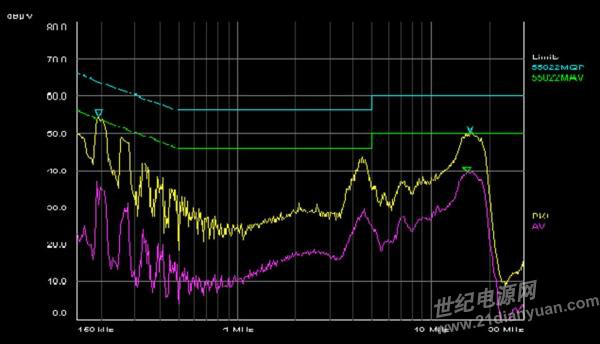

现象 (测试时输出 GND 与大地连接) 是:

冷机

热机

从以上波形可以看出,热机后在 15~16MHz 的传导变差很多。裕量不足,需要整改,目标是达到≥10dB 的裕量。现象分析

▪ 传导在10几 MHz 的高频处超标,一般是共模干扰超标引起的。

▪ 测试是输出与地连接的情况下超了,说明地线参与了耦合干扰,从这也证明了这是共模干扰超标。

此共模干扰从源端产生,经变压器的一二次侧寄生电容传到次级,一部分被 Y 电容传回原边,另一部分经过输出端的共模阻隔后通过负载的接地线传到 LISN。

根据以上分析以及共模路径图,建立如下模型:

其中:

Z2 为变压器一二次侧寄生电容的阻抗;

Z3 为 Y 电容和所串的磁珠的阻抗;

Z4 为输出共模的阻抗;

Z5 为 LISN 的阻抗。

从以上模型图可以得知:

① 要降低共模干扰 Vlisn,有多种方法,比如降低 Vnoise、增大 Z2、减小 Z3、增大 Z4。

② 降低 Vnoise 就是从源端解决了,一般会影响效率,改动太大。

③ 增大 Z2,就是减小变压器一二次侧寄生电容,这个目前已是比较优化的结构,改动效果不明显。

④ 减小 Z3,可以通过增大 Y 电容实现。

⑤ 增加 Z4,就是提升输出共模的阻抗。

方法建议

经过实测,增大 Y 电容可以降 5dB,但会导致漏电流超出客户规格,无法导入。

那就看增加 Z4 阻抗了,其实热机后会变差也是由于 Z4 的阻抗特性发生了变化,尝试过降低 Z4 的温度,但由于电流较大,温度仍然较高,效果不明显。

难道没办法了吗?

细看模型,Z3 回路还包括磁珠的阻抗,是否可以通过去掉磁珠来解决呢?

下面去掉后的实测效果:

结果是改善3~4dB,虽然没有加大 Y 电容的效果好,但有足够的裕量了,同时不影响效率,还降低了成本,两全其美啊!

其实,还要去确认辐射。结果辐射在 30M~40M 的地方变差了 2dB。好在即使变差也有足够的裕量,不用再去头疼了。至此,问题解决!

此帖通过分析、建模和最后验证,说明了传导整改是有章可循的,有了理论指导,实践起来就会事半功倍。 案例本身不难,希望是通过例子能够举一反三,在整改中发挥作用。 技术这东西,说穿了就那么回事,在没说穿的时候又有多少人可以自己看穿。

* 查看更多内容,下载仿真文件,请点击进入 21Dianyuan 社区

* 本文为21Dianyuan 社区原创文章,未经授权禁止转载。请尊重知识产权,违者本司保留追究责任的权利。

免责声明:本文若是转载新闻稿,转载此文目的是在于传递更多的信息,版权归原作者所有。文章所用文字、图片、视频等素材如涉及作品版权问题,请联系本网编辑予以删除。

我要投稿

近期活动

- 安森美汽车&能源基础设施白皮书下载活动时间:2024年04月01日 - 2024年10月31日[立即参与]

- 2023年安森美(onsemi)在线答题活动时间:2023年09月01日 - 2023年09月30日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年08月01日 - 2023年08月31日[查看回顾]

- 【在线答题活动】PI 智能家居热门产品,带您领略科技智慧家庭时间:2023年06月15日 - 2023年07月15日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年06月01日 - 2023年06月30日[查看回顾]

分类排行榜

- 汽车电子电源行业可靠性要求,你了解多少?

- 内置可编程模拟功能的新型 Renesas Synergy™ 低功耗 S1JA 微控制器

- Vishay 推出高集成度且符合 IrDA® 标准的红外收发器模块

- ROHM 发布全新车载升降压电源芯片组

- 艾迈斯半导体推出行业超薄的接近/颜色传感器模块,助力实现无边框智能手机设计

- 艾迈斯半导体与 Qualcomm Technologies 集中工程优势开发适用于手机 3D 应用的主动式立体视觉解决方案

- 维谛技术(Vertiv)同时亮相南北两大高端峰会,精彩亮点不容错过

- 缤特力推出全新商务系列耳机 助力解决开放式办公的噪音难题

- CISSOID 和泰科天润(GPT)达成战略合作协议,携手推动碳化硅功率器件的广泛应用

- 瑞萨电子推出 R-Car E3 SoC,为汽车大显示屏仪表盘带来高端3D 图形处理性能

编辑推荐

小型化和稳定性如何兼得?ROHM 推出超小型高输出线性 LED 驱动器 IC,为插座型 LED 驱动 IC 装上一颗强有力的 “心脏”

众所周知,LED的驱动IC担负着在输入电压不稳定的情况下,为LED提供恒定的电流,并控制恒定(可调)亮度的作用。无论是室内照明,还是车载应用,都肩负着极为重要的使命。

- 关于反激电源效率的一个疑问

时间:2022-07-12 浏览量:9992

- 面对热拔插阐述的瞬间大电流怎么解决

时间:2022-07-11 浏览量:8762

- PFC电路对N线进行电压采样的目的是什么

时间:2022-07-08 浏览量:9396

- RCD中的C对反激稳定性有何影响

时间:2022-07-07 浏览量:7064

- 36W单反激 传导7~10M 热机5分钟后超标 不知道哪里出了问题

时间:2022-07-07 浏览量:5815

- PFC电感计算

时间:2022-07-06 浏览量:4048

- 多相同步BUCK

时间:2010-10-03 浏览量:37822

- 大家来讨论 系列之二:开机浪涌电流究竟多大?

时间:2016-01-12 浏览量:43112

- 目前世界超NB的65W适配器

时间:2016-09-28 浏览量:59984

- 精讲双管正激电源

时间:2016-11-25 浏览量:127831

- 利用ANSYS Maxwell深入探究软磁体之----电感变压器

时间:2016-09-20 浏览量:107483

- 【文原创】认真的写了一篇基于SG3525的推挽,附有详细..

时间:2015-08-27 浏览量:100139