SDSoC 开发流程探秘:简单背后的不简单

摘要:在上SDSoC系列文章的上一篇中,我们已经介绍了如何在SDSoC中构建硬件和软件平台,并使用SDSPFM工具生成客户应用开发平台(参见《SDSoC开发起步:构建硬件和软件平台》)。

在上SDSoC系列文章的上一篇中,我们已经介绍了如何在SDSoC中构建硬件和软件平台,并使用SDSPFM工具生成客户应用开发平台(参见《SDSoC开发起步:构建硬件和软件平台》)。如果你已经完成了上述工作,恭喜你——现在你可以正式“起步”开始基于SDSoC在Zynq SoC上开发自己的应用了!

一个典型的SDSoC设计开发流程,包括以下几个步骤:

用户定义开发应用所需的目标平台。

用户基于C/C++设计和验证算法。

用户根据系统特征描述确定性能瓶颈,然后进行软硬件分区。

SDSoC将自动执行那些通过PL(可编程逻辑)加速的功能,其他功能保留在PS(处理器系统)中。

SDSoC也将自动生成软/硬件之间的连接和DataMover逻辑以连接PL和PS中的功能。

如果最终的结果未达到设计要求,开发者可以重新进行软硬件功能分区,探索最优的系统架构。

图1,SDSoC典型开发流程(图片来源:赛灵思)

没错,使用SDSoC进行应用开发说起来就是这么简单的几步。我们这篇文章的内容完全可以在这里划上句号。

不过,我们还是希望将现在“简单”的设计流程,和传统上可编程逻辑“不简单”的设计流程进行一个对比,让大家深刻认识到SDSoC到底帮你做了些什么?

所谓“没有对比就没有伤害”,传统的Zynq SoC开发流程是复杂成这个样子的——首先由系统架构工程师对软硬件进行分区,即确定哪些功能放入PL(可编程逻辑)中进行硬件加速,哪些功能在PS(处理器系统)中用软件实现;

接下来,硬件工程师基于Vivado生成要在PL中加速的IP并搭建硬件平台,还要完成软/硬件之间的连接,配置PS与PL之间的接口工作等;然后将硬件平台的数据导入SDK,由软件工程师完成配套的的驱动和应用程序的开发。可见,传统的设计流程,需要很多团队和资源的介入,不简单。

而如果完成了上述设计工作之后,发现系统架构还需要优化,这就悲催了——设计不得不重新调整软硬件分区,上述整个开发流程又要重新进行一遍,而且很多情况下需要多次迭代才能找到那个令人满意的系统架构和方案。由此耗费的时间和资源,是巨大的,甚至是不可控的。

图2,传统的FPGA SoC应用开发流程(图片来源:赛灵思)

而使用SDSoC之后,很多工作是由工具自动完成的:省去了诸如软件驱动和硬件连接等繁复的手动工作,同时使用C/C++终端应用可以像函数调用一样输入调用用户算法IP;只需要单次点击,就可以完成分区设置以确定需要在可编程逻辑中运行的功能。

图3,使用SDSoC简化后的FPGA SoC应用开发流程(图片来源:赛灵思)

做一个不是十分准确的比喻:SDSoC与传统工具和开发流程的差别,就像是自动挡与手动挡汽车的不同,它让复杂的工作对用户变得“透明”,让用户实际的“操作”变得更简单,而用户由此被解放出来的精力,则可以用到思考“要去哪儿、如何走”等更高级的问题,而不是和“油离配合”较劲儿。

类比到FPGA SoC的应用开发中,用户最关注的部分往往是算法的最终实现和算法模块的优化——包括IP或是软件功能块——SDSoC的设计理念正是让用户能够更加专注于这些核心问题,其他问题SDSoC帮你搞掂。从这个意义上看,SDSoC在“简单”的背后确实不简单。

- 安森美汽车&能源基础设施白皮书下载活动时间:2024年04月01日 - 2024年10月31日[立即参与]

- 2023年安森美(onsemi)在线答题活动时间:2023年09月01日 - 2023年09月30日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年08月01日 - 2023年08月31日[查看回顾]

- 【在线答题活动】PI 智能家居热门产品,带您领略科技智慧家庭时间:2023年06月15日 - 2023年07月15日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年06月01日 - 2023年06月30日[查看回顾]

- 汽车电子电源行业可靠性要求,你了解多少?

- 内置可编程模拟功能的新型 Renesas Synergy™ 低功耗 S1JA 微控制器

- Vishay 推出高集成度且符合 IrDA® 标准的红外收发器模块

- ROHM 发布全新车载升降压电源芯片组

- 艾迈斯半导体推出行业超薄的接近/颜色传感器模块,助力实现无边框智能手机设计

- 艾迈斯半导体与 Qualcomm Technologies 集中工程优势开发适用于手机 3D 应用的主动式立体视觉解决方案

- 维谛技术(Vertiv)同时亮相南北两大高端峰会,精彩亮点不容错过

- 缤特力推出全新商务系列耳机 助力解决开放式办公的噪音难题

- CISSOID 和泰科天润(GPT)达成战略合作协议,携手推动碳化硅功率器件的广泛应用

- 瑞萨电子推出 R-Car E3 SoC,为汽车大显示屏仪表盘带来高端3D 图形处理性能

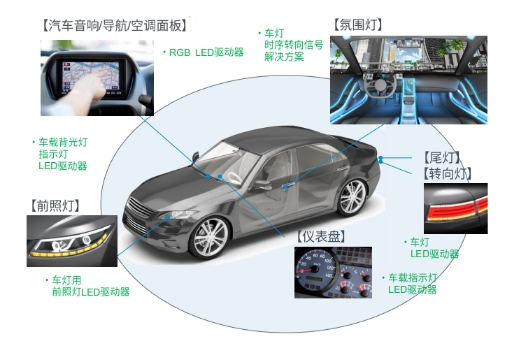

众所周知,LED的驱动IC担负着在输入电压不稳定的情况下,为LED提供恒定的电流,并控制恒定(可调)亮度的作用。无论是室内照明,还是车载应用,都肩负着极为重要的使命。

- 关于反激电源效率的一个疑问

时间:2022-07-12 浏览量:10105

- 面对热拔插阐述的瞬间大电流怎么解决

时间:2022-07-11 浏览量:8872

- PFC电路对N线进行电压采样的目的是什么

时间:2022-07-08 浏览量:9501

- RCD中的C对反激稳定性有何影响

时间:2022-07-07 浏览量:7139

- 36W单反激 传导7~10M 热机5分钟后超标 不知道哪里出了问题

时间:2022-07-07 浏览量:5917

- PFC电感计算

时间:2022-07-06 浏览量:4126

- 多相同步BUCK

时间:2010-10-03 浏览量:37846

- 大家来讨论 系列之二:开机浪涌电流究竟多大?

时间:2016-01-12 浏览量:43142

- 目前世界超NB的65W适配器

时间:2016-09-28 浏览量:60004

- 精讲双管正激电源

时间:2016-11-25 浏览量:127997

- 利用ANSYS Maxwell深入探究软磁体之----电感变压器

时间:2016-09-20 浏览量:107525

- 【文原创】认真的写了一篇基于SG3525的推挽,附有详细..

时间:2015-08-27 浏览量:100223