ASML可支撑摩尔定律延续到2030年!台积电将研发1.5nm制程工艺?

摘要:早在2017年初,就有媒体提到,继7nm制程工艺问世之后,接着各大厂商会争相开发5nm工艺,再到3nm工艺。那么在更遥远的未来呢?

早在2017年初,就有媒体提到,继7nm制程工艺问世之后,接着各大厂商会争相开发5nm工艺,再到3nm工艺。那么在更遥远的未来呢?光刻机制造商ASML的CEO Peter Wennink当初在接受媒体的采访时则表示,EUV(极紫外光刻机)工艺不仅能帮助下游的厂商降低7nm、5nm的工艺成本,还可支撑芯片制造业到2030年前后的工艺;并且在当时就已经有客户在讨论和研究未来的1.5nm工艺方案和路线图了。

而之前,包括英特尔、台积电等在内的高层,以及行业中的专家和工程师们,大都都对3nm及其以下的工艺持相当保守的观点。台积电的创始人张忠谋2017年9月在公开场合讲出,起码在未来10年中,摩尔定律在半导体行业中依然不会失效。台积电完全能够研发出5nm制程和3nm制程。但要研发出2nm及其以下制程,会面临很高的难度。台积电要不要研发2nm及其以下制程技术,还要再等几年才能确定结果。并且,台积电在未来会投产3nm制程。但包括张忠谋等台积电的高管们也都在忧心,3nm制程的生产成本其实不算低,今后台积电的3nm制程会有多大市场,尚没法评估出来。

业内人士分析,英特尔、台积电和三星等厂商之所以争抢ASML的EUV光刻机,主要是因为EUV光刻机有三点优势。首先,对晶圆制造商而言,单次EUV曝光可以取代3次或更多次的光学曝光,每个掩模层可以节省大约1.5天的时间。其次,厂商在创建图案时使用多个掩膜会导致EPE的增加,而将多个光学掩模简化为单个EUV掩模可以将EPE减少高达90%。再则,EUV能够帮助厂商创建出比多重图形曝光技术更一致和更清晰的图案,从而能够实现更严格的电气参数分布。在某些情况下,厂商采用EUV光刻机的确能够起到节约成本的效果。

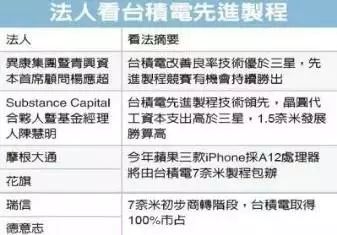

日前,据台湾媒体报道,摩根大通最新发布的一份报告显示,摩尔定律出现重大突破。ASML确认了1.5nm制程工艺的发展性,并可支撑摩尔定律延续至2030年。分析师还预期,台积电与三星新一轮的制程工艺竞赛将围绕1.5nm展开,并且台积电具有技术领先的优势,稳赢三星的概率大。摩根大通科技产业研究部的主管哈戈谷指出,ASML当前更加坚定摩尔定律可延伸至1.5nm工艺,以支撑半导体产业至少发展至2030年。

另外,ASML将在3nm与更先进的制程采用高数值孔径(NA)光学系统;过去,ASML为发展NA系统,收购了卡尔蔡司旗下的子公司蔡司半导体。如今,外资圈内已经有人证实,ASML将拓展3nm及其以下的制程技术。

Substance Capital的合伙人陈慧明指出,台积电之所以能在行业中长期保持龙头地位,靠的是不断推进自己的制程工艺进步。因此,ASML开展研究1.5nm工艺制程技术,有利于台积电继续巩固自身在晶圆代工行业中优势。异康集团暨青兴资本的首席顾问杨应超称,ASML在技术上的进展是半导体芯片行业中的一大突破,对整个大产业会产生积极的效果。现在台积电与三星之间正围绕着7nm制程工艺激烈开打,今后两者之间在制程技术上的竞争料将更为激烈。

- 安森美汽车&能源基础设施白皮书下载活动时间:2024年04月01日 - 2024年10月31日[立即参与]

- 2023年安森美(onsemi)在线答题活动时间:2023年09月01日 - 2023年09月30日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年08月01日 - 2023年08月31日[查看回顾]

- 【在线答题活动】PI 智能家居热门产品,带您领略科技智慧家庭时间:2023年06月15日 - 2023年07月15日[查看回顾]

- 2023年安森美(onsemi)在线答题活动时间:2023年06月01日 - 2023年06月30日[查看回顾]

- 汽车电子电源行业可靠性要求,你了解多少?

- 内置可编程模拟功能的新型 Renesas Synergy™ 低功耗 S1JA 微控制器

- Vishay 推出高集成度且符合 IrDA® 标准的红外收发器模块

- ROHM 发布全新车载升降压电源芯片组

- 艾迈斯半导体推出行业超薄的接近/颜色传感器模块,助力实现无边框智能手机设计

- 艾迈斯半导体与 Qualcomm Technologies 集中工程优势开发适用于手机 3D 应用的主动式立体视觉解决方案

- 维谛技术(Vertiv)同时亮相南北两大高端峰会,精彩亮点不容错过

- 缤特力推出全新商务系列耳机 助力解决开放式办公的噪音难题

- CISSOID 和泰科天润(GPT)达成战略合作协议,携手推动碳化硅功率器件的广泛应用

- 瑞萨电子推出 R-Car E3 SoC,为汽车大显示屏仪表盘带来高端3D 图形处理性能

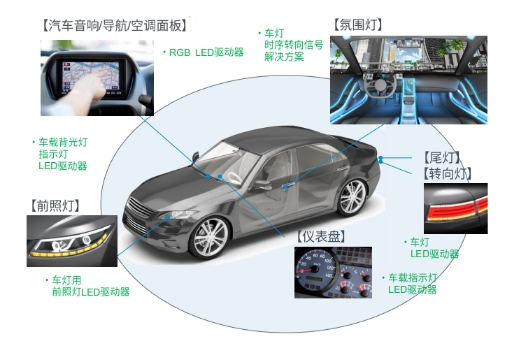

众所周知,LED的驱动IC担负着在输入电压不稳定的情况下,为LED提供恒定的电流,并控制恒定(可调)亮度的作用。无论是室内照明,还是车载应用,都肩负着极为重要的使命。

- 关于反激电源效率的一个疑问

时间:2022-07-12 浏览量:9992

- 面对热拔插阐述的瞬间大电流怎么解决

时间:2022-07-11 浏览量:8763

- PFC电路对N线进行电压采样的目的是什么

时间:2022-07-08 浏览量:9396

- RCD中的C对反激稳定性有何影响

时间:2022-07-07 浏览量:7064

- 36W单反激 传导7~10M 热机5分钟后超标 不知道哪里出了问题

时间:2022-07-07 浏览量:5815

- PFC电感计算

时间:2022-07-06 浏览量:4048

- 多相同步BUCK

时间:2010-10-03 浏览量:37822

- 大家来讨论 系列之二:开机浪涌电流究竟多大?

时间:2016-01-12 浏览量:43112

- 目前世界超NB的65W适配器

时间:2016-09-28 浏览量:59984

- 精讲双管正激电源

时间:2016-11-25 浏览量:127838

- 利用ANSYS Maxwell深入探究软磁体之----电感变压器

时间:2016-09-20 浏览量:107483

- 【文原创】认真的写了一篇基于SG3525的推挽,附有详细..

时间:2015-08-27 浏览量:100141